ОБЗОРЫ

Архитектура PowerPC используется в нескольких семействах микропроцессоров

Ключевую роль в создании семейства микропроцессоров PowerPC сыграла корпорация IBM (www.ibm.com). Дело в том, что за основу создаваемого семейства был взят ее процессор POWER (Performance Optimization With Enhanced RISC). Стоит отметить, что существенный вклад в развитие фундаментальной концепции RISC-архитектуры внесли ученые из Исследовательского центра IBM, где в середине 70-х годов был разработан мини-компьютер IBM 801. Дальнейшее развитие этих идей нашло отражение при создании концепции POWER в конце 80-х. Впоследствии именно данная архитектура стала основой нескольких семейств рабочих станций и серверов корпорации.

POWER во многих отношениях представляет собой традиционную RISC-архитектуру. В ней сохранены наиболее важные отличительные особенности RISC: фиксированная длина команд, простые способы адресации и команд, большой размер регистрового файла, а также и 3-операндный формат инструкций. Однако архитектура POWER имеет несколько дополнительных свойств, которые отличают ее от других RISC-архитектур.

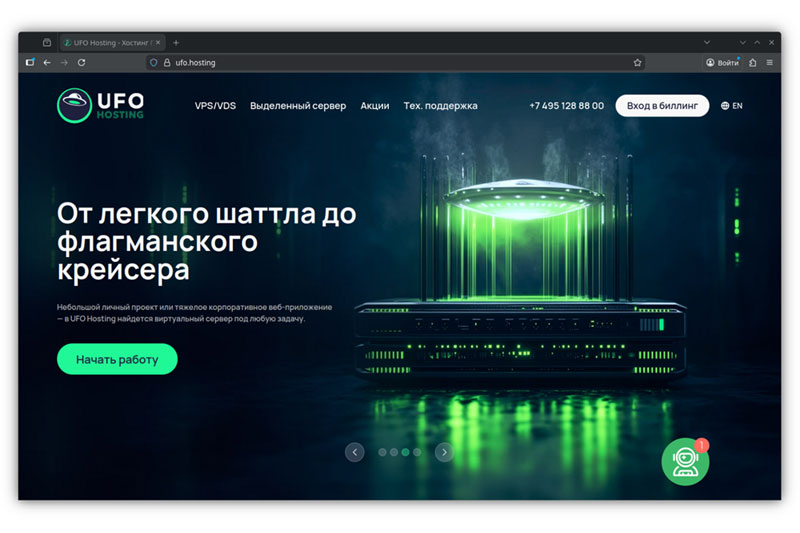

Микропроцессор PowerPC 750

Ее набор команд изначально был основан на идее суперскалярной обработки. В базовой архитектуре команды распределяются по трем независимым исполнительным устройствам: целочисленной и вещественной арифметики, а также переходов. Для сокращения времени выполнения в POWER были введены специальные команды групповой загрузки и записи, которые обеспечивали пересылку содержимого нескольких регистров в памяти (и обратно) с помощью единственной команды. Архитектура переходов POWER была организована с учетом их предварительного просмотра и методики свертывания. Кстати, реализация условных переходов, используемая в архитектуре POWER, является ее уникальным свойством по сравнению с другими RISC-процессорами.

Первая аппаратная реализация POWER появилась на рынке в 1990 г. С тех пор IBM представила еще несколько версий процессоров (POWER2, POWER2+, POWER3, POWER3-II), обеспечивающих поддержку кэш-памяти второго уровня и имеющих расширенный набор команд.

PowerPC положила начало однокристальной архитектуре POWER. Кроме того, в ней было сделано несколько упрощений с целью приспособления для однокристальных процессоров: исключены команды, которые могли бы стать препятствием повышения тактовой частоты; устранены архитектурные препятствия суперскалярной обработке и внеочередному выполнению команд; добавлены свойства, необходимые для поддержки симметричной многопроцессорной обработки; ее разрядность расширена до 64. Отметим, что PowerPC поддерживает ту же самую базовую модель программирования и назначение кодов операций команд, что и архитектура POWER.

Плоды триумвирата

Итак, осенью 1991 г. три известные корпорации - Apple, IBM и Motorola сообщили о решении создать семейство RISC-процессоров для широкого спектра областей применения. Предполагалось, что данные кристаллы будут использоваться на компьютерах, начиная от серверов верхнего уровня и рабочих станций до настольных ПК. Проект был рассчитан на 10 лет, но первенец семейства - процессор под торговой маркой PowerPC 601 появился уже в 1993 г. Он имел 32-разрядную внутреннюю структуру и размещался на кристалле прощадью 121 кв. мм. Общее количество транзисторов составляло 2,8 млн. Были выпущены модели с тактовыми частотами 50, 66, 80 МГц. На кристалле PowerPC 601 находилось три исполнительных устройства: целочисленное, вещественной арифметики и блок обработки переходов. Все три устройства работали параллельно и в значительной степени независимо. Благодаря суперскалярной архитектуре за один такт могло выполняться до трех команд одновременно. Процессор оперировал с 8-, 16-, 32-разрядными целыми числами, а также с 32-, 64-разрядными числами с плавающей запятой. На кристалле располагались раздельная кэш-память команд и данных объемом 32 Кб (16+16) и устройство управления памятью. Процессор имел 64-разрядную шину данных и 32-разрядную шину адресов.

Уже в 1994 г. появился следующий процессор семейства. Им стал PowerPC 603. Структура этого процессора копировала структуру PowerPC 601. Но он размещался на кристалле площадью 85,1 кв. мм и был изготовлен с учетом проектных норм 0,5 мкм на 1,6 млн. транзисторов. Потребляемая мощность процессора, работавшего на частоте 80 МГц, не превышала 2,5 Вт. Данное устройство во многом представляло собой упрощенную версию предыдущего. Оно выполняло не более двух команд за один такт, а размер кэш-памяти равнялся всего 8 Кб (4+4).

В 1995 г. вышла улучшенная версия данного процессора под маркой PowerPC 603e. У этого кристалла производительность была увеличена. Первоначально он выпускался с тактовыми частотами 80 и 100 МГц. В настоящее время такие кристаллы находят применение в качестве встраиваемых микропроцессоров. Их тактовые частоты составляют 100, 166 и 200 МГц.

При использовании проектных норм 0,5 мкм процессор размещался на кристалле площадью 98 кв. мм и содержал 2,8 млн. транзисторов. На частоте 100 МГц он потреблял примерно 3,2 Вт. Еще одной новинкой в этом процессоре стало появление трех энергосберегающих режимов, а также устройства динамического управления энергопотреблением. При использовании проектных норм 0,35 мкм площадь кристалла уменьшается до 79 кв. мм.

Одновременно с PowerPC 603e появился кристалл PowerPC 602 для портативных компьютеров, выполненный с учетом проектных норм 0,5 мкм. На кристалле площадью 50 кв. мм размещалось до 1 млн. транзисторов. Шины адреса и данных устройства были мультиплексированы. Иными словами, сначала процессор выводил на шину адрес и специальным сигналом информировал об этом все устройства, а затем по той же шине передавал данные. Доступ к памяти осуществлялся в пакетном режиме, что делало снижение производительности процессора не столь ощутимым.

К трем основным исполнительным устройствам добавили еще одно - формирования адресов доступа к памяти. Тем не менее структура блоков процессора упростилась по сравнению с PowerPC 603. Так, устройство для операций вещественной арифметики могло обрабатывать только 32-разрядные числа (в предыдущих - 64-разрядные). Количество производимых за один такт операций сократилось до одной, что уменьшило размер блока декодирования и упростило схему предсказания ветвления. Также исключили сложные графические и строковые операции, благодаря чему упростилось устройство формирования адресов. Оставшиеся операции пересылки были оптимизированы и выполнялись за один такт. Кэш-память команд и данных составляли теперь по 2 Кб (впоследствии 4 Кб) каждая. Процессор имел быстрый механизм защиты памяти и все режимы энергосбережения, как у PowerPC 603.

В конце 1996 г. была анонсирована еще одна модель - PowerPC 603ev с тактовой частотой 166 МГц (180 и 200 МГц). Кристалл производился с соблюдением проектных норм 0,35 мкм. В нем были усовершенствованы блоки операций деления и управления кэш-памятью.

Последним 32-разрядным процессором этого семейства стал PowerPC 604. Он был анонсирован в конце 1995 г. Процессор построен по технологии 0,35 мкм и работал на тактовых частотах 100, 120, 133 и 150 МГц. Усовершенствованный вариант этого процессора - PowerPC 604e, выполненный с использованием того же технологического процесса. Он на кристалле площадью 148 кв. мм содержал 5,1 млн. транзисторов. Были выпущены микросхемы, работающие на тактовых частотах 167, 180, 200, а затем и 332 МГц. Внутренняя кэш-память на кристалле возросла вдвое - 32 Кб для команд и 32 Кб для данных.

В 1995 г. вышел первый 64-разрядный процессор семейства - PowerPC 620, предназначенный для рабочих станций и высокопроизводительных серверов. Этот кристалл имел шесть уже независимых исполнительных устройств и встроенную кэш-память на 64 Кб (32+32). Микросхема производилась с учетом проектных норм 0,5 мкм на кристалле площадью 311 кв. мм и содержала 7 млн. транзисторов. В процессоре использовалась четырехконвейерная суперскалярная архитектура с шестью исполнительными устройствами: тремя блоками целочисленной арифметики, одним блоком для операций с плавающей точкой, блоком загрузки/сохранения и блоком переходов. За один такт процессор мог выполнять до четырех команд. Шинный интерфейс кристалла включал унифицированную внутреннюю поддержку кэш-памяти второго уровня объемом до 128 Мб.

Своей дорогой

К сожалению, корпорации Motorola и IBM строили совершенно разные планы относительно микропроцессоров PowerPC. Так, IBM все больше ориентировала свои кристаллы на собственные серверы и рабочие станции. В то же время Motorola, хотя и продолжала производить 32-разрядные микросхемы для компьютеров Apple, стала прощупывать возможности применения PowerPC в коммуникационном оборудовании.

В июне 1998 г. IBM и Motorola объявили о том, что совместное предприятие - центр проектирования PowerPC (известный под названием Somerset) полностью перешел к корпорации Motorola. Это произошло в связи с разным видением руководства компаний будущего PowerPC. В частности, IBM решила сосредоточиться на производстве быстрых микропроцессоров с технологией медных межсоединений.

Первым микропроцессором IBM с медными межсоединениями в 1998 г. стал кристалл PowerPC 750. Вообще говоря, по сравнению с технологией, где межсоединения элементов выполнены на основе алюминия, медь позволяет сделать кристалл меньше и быстрее. Медная металлизация уменьшает общее сопротивление, что позволяет увеличить скорость работы кристалла на 15-20%. Обычно технология дополняется еще одной новинкой - технологией “кремний на изоляторе” (SOI, Silicon On Insulator). Она уменьшает паразитные емкости, возникающие между элементами микросхемы и подложкой, благодаря чему также увеличивается тактовая частота транзисторов, а скорость повышается на 20-30%. То есть общий рост производительности в идеальном случае может достигнуть 50%. Уже через год IBM объявила о том, что ею продано более 1 млн. микропроцессоров PowerPC с медными межсоединениями. Таким образом, среди ряда крупнейших фирм, выпускающих полупроводниковые приборы, IBM стала первым производителем микропроцессоров и микроконтроллеров с медными межсоединениями (технологический процесс CMOS7S).

Одной из особенностей PowerPC 750 была отличная от используемой в предыдущих версиях PowerPC схема кэширования. Микросхема имела выделенную шину, с помощью которой кэш-память второго уровня (емкостью 0,5; 1 или 2 Мб) подсоединялась непосредственно к кристаллу (такая схема кэширования называется Back Side), а не через системную шину. При этом выделенная шина работала на удвоенной тактовой частоте (системной шины), благодаря чему появлялась возможность использования микросхем памяти типа SRAM 233 МГц. Кристаллы PowerPC 750, работающие на тактовых частотах от 200 до 500 МГц, выполнялись с учетом проектных норм 0,25 (PID8t) и 0,22 (PID8p) мкм.

Версия микропроцессора PowerPC 750CX отличалась наличием встроенной двухвходовой наборно-ассоциативной 256-килобайтовой кэш-памяти. Отметим, что восьмивходовая наборно-ассоциативная кэш-память первого уровня для команд и данных имеет объем по 32 Кб каждая. Кристалл выполнен с учетом проектных норм 0,18 мкм, с шестислойной медной металлизацией. Рабочие тактовые частоты составляют 366, 400 и 466 МГц.

В феврале этого года IBM сообщила о разработке модели PowerPC 750CXe, которая названа корпорацией “самым производительным процессором из серии PowerPC”. Кристалл PowerPC 750CXe содержит 256 Кб встроенной кэш-памяти второго уровня и изготовлен с использованием медных межсоединений и с соблюдением проектных норм 0,18 мкм. IBM уже запустила в массовое производство PowerPC 750CXe с тактовыми частотами 400, 500 и 600 МГц, их поставки начнутся в апреле. Образцы 700 МГц кристаллов появятся в мае. По имеющейся информации, корпорация Apple уже планирует встраивать данные процессоры в свои компьютеры G3 iMac.

В заключение стоит отметить, что архитектура POWER в этом году получит развитие в новом процессоре Power4. Эта микросхема, вообще говоря, содержит два процессора, разделяющих общую кэш-память второго уровня с пропускной способностью свыше 100 Гб/с. Связь процессоров с кэш-памятью второго уровня, равно как и с другими микросхемами, осуществляется посредством коммутатора (55 Гб/с). Для обеспечения когерентности кэш-памяти и пересылки данных в кэш-память второго уровня применяется специальный протокол.

Оба процессора Power4 имеют два конвейерных блока для работы с 64-разрядными операндами с плавающей запятой на частоте 1 ГГц. В процессорах реализуется внеочередное исполнение команд. Они содержат раздельные кэш-памяти команд и данных первого уровня емкостью по 64 Кб каждая. Кроме разделяемой кэш-памяти на кристалле второго уровня допускается применение внешней кэш-памяти третьего уровня. Для образования мультипроцессорных конфигураций имеются три канала с суммарной пропускной способностью 45 Гб/с.

Микропроцессор будет реализован на кристалле площадью 400 кв. мм, содержащем 170 млн. транзисторов. Он создается с соблюдением проектных норм 0,18 мкм, использованием технологии SOI и пятислойной медной металлизации. Для организации SMP-систем планируется помещать четыре микросхемы (восемь процессоров) в один MCM-модуль (Multi-chip Ceramic Module).