На пути в третье тысячелетие

Александр Ливеровский

В 1964 г., через шесть лет после изобретения интегральной схемы, один из основателей корпорации Intel Гордон Мур высказал предположение, что число транзисторов в кристалле будет удваиваться каждые полтора года. Это утверждение получило название первого закона Мура. Достаточно взглянуть на рис. 1, чтобы убедиться в его справедливости. С тех пор и до настоящего времени этот закон не нарушается, и есть все основания предполагать, что и в ближайшие 10 лет положение не изменится. Альберт Ю, руководитель корпорации Intel по микропроцессорным продуктам, предсказывает, что к 2006 г. число транзисторов на кристалле достигнет 350 млн., тактовая частота - 4 ГГц, а производительность - 20 000 млн. команд в секунду (MIPS).

К несчастью, действует и второй закон Мура, который гласит, что стоимость фабрик по производству микросхем экспоненциально возрастает с усложнением кристаллов. Так, стоимость фабрики, на которой корпорация Intel производила микросхемы динамической памяти емкостью 1 Кбит, составляла 4 млн. долл., а оборудование по производству микропроцессора Pentium по 0,6-микронной технологии c 5,5 млн. транзисторов обошлось в 2 млрд. долл.

Стоимость же завода по производству микросхем по 0,1-микронной технологии оценивается в 10 млрд. долл., и это обстоятельство может повлиять на воплощение первого закона Мура в жизнь.

Немного истории

Мы не будем возвращаться к истокам микропроцессорной техники, а начнем с того момента, когда микропроцессоры стали 16-разрядными и в них начали применяться методы, ранее использовавшиеся в больших машинах.

В 1978 г. корпорация Intel выпустила 16-разрядный микропроцессор i8086, которому суждено было стать основой персональных компьютеров, так сильно изменивших наш мир. В нем еще не было заметно влияния больших машин и мини-компьютеров. На следующий год появился 16-разрядный процессор Z8000 компании Zilog с сегментной организацией памяти. В том же году Motorola выпустила на рынок свой 32-разрядный процессор MC68000. Хотя арифметика процессора MC68000 была на самом деле 16-разрядной, программист этого не замечал, так как все 16 регистров процессора были 32-разрядными и арифметические операции так же выполнялись с 32- разрядными операндами. Он имел все предпосылки стать сердцем будущих ПК. Но этого не произошло. По не вполне ясным причинам IBM выбрала для своего компьютера IBM PC, который появился в 1981 г., процессор i8088, а не MC68000.

В 1981 г., после многочисленных отсрочек, Intel выпустила универсальный 32-разрядный процессор iAPX432, чья защита памяти базировалась на тегах. Ранее подобные методы использовались в больших машинах, а именно в машине университета Rice (1959 г.), в машинах B5000 и B5500 корпорации Burroughs (1961 г.), в компьютере S38 корпорации IBM (1975 г.) и ряде других.

Два процессора iAPX432 могли работать параллельно и проверять друг друга. Но пробелы в архитектуре и другие проблемы привели к тому, что этот процессор был тихо забыт, а Intel сосредоточилась на 16-разрядном процессоре i80286, который появился в 1982 г. Процессор работал в двух режимах: в режиме 8086 и в защищенном. В нем была организована сегментная организация памяти с четырьмя уровнями, или “кольцами” защиты, набор команд был расширен и процессор стал намного быстрее i8086. Однако в новом режиме старые программы выполнять было нельзя, и не только потому, что некоторые команды в защищенном режиме выполнялись не так, как в i8086 (например, PUSH SP, а всего таких команд было 14), а потому, что дескрипторы сегментов этого не допускали. Тем не менее он с большим успехом использовался в PC/AT, в режиме быстрого i8086 с операционной системой DOS корпорации Microsoft.

Содружество IBM, Microsoft и Intel и громадный объем программ, написанных для DOS, фактически закрыли дорогу на рынок ПК многим производителям микропроцессоров.

В 1983 г. Zilog создала микропроцессор Z8003, поддерживающий виртуальную память со страничной организацией. В том же году компания объявила о предстоящем выпуске 32-разрядного процессора Z80000 и издала подробное его описание. Этот процессор поддерживал виртуальную память с сегментно-страничной организацией и имел внутреннюю кэш-память и буфер быстрой переадресации (TLB). Но поставки его начались только в 1986 г. - на год позже 32-разрядного процессора Intel i386, он и не смог пробиться на рынок.

Первым микропроцессором с встроенной кэш-памятью (впервые примененной в IBM 360/85 в 1969 г.) был процессор компании Motorola MC68020 (1984 г.)

Разрабатывались и другие процессоры. Так, корпорация National в 1980 г. выпустила 16-разрядный процессор 32016, за которым в 1982 г. последовал 32-разрядный 32032, а затем 32332 (1985 г.) и 32532 (1987 г.). Интересной особенностью этих процессоров была поддержка модульности программы и разделения памяти. В процессоре среди восьми специальных регистров имелся регистр, в котором содержался адрес дескриптора исполняемого в настоящий момент модуля. В дескрипторе имелся адрес таблицы компоновки модуля. Элементом таблицы мог быть либо адрес внешней переменной, либо номер модуля и смещение точки входа в него относительно его начала. Команда вызова внешней процедуры использовала эту пару для передачи управления.

Адрес внешней переменной в этой таблице можно было использовать для совместной работы с данными из разных модулей в режиме “внешней” адресации.

Архитектура этого микропроцессора была весьма элегантной, но и эта линия микропроцессоров не получила широкого распространения, и к 1989 г. выпуск их был прекращен.

После того как корпорация AT&T в 1981 г. была разделена правительством США на семь независимых компаний, ей было разрешено выпускать компьютеры на продажу, на что ранее она права не имела.

Была создана серия микропроцессоров WE32000 (1985 г.), также с весьма интересной архитектурой, разработанной в лаборатории Bell. Так, например, эта архитектура непосредственно поддерживала концепцию процесса. В наборе команд имелась команда вызова процесса, при выполнении которой из блока управления процессом брался контекст нового процесса.

И эта серия также не получила широкого распространения.

Только Motorola добилась успеха. Ее процессоры стали применяться в рабочих станциях Apollo и Sun (1982 г.) и в персональных компьютерах Apple Macintosh (1984 г.).

Хотя Уилкс еще в 1951 г. предложил микропрограммный способ выполнения команд, при котором управление их выполнением базировалось на постоянной памяти, организованной в виде прямоугольной матрицы, где каждая строка соответствовала одному машинному такту, а элементы в столбце управляли вентилями, тем не менее на заре развития вычислительной техники господствовал аппаратный способ управления выполнением команд.

Использование микропрограммирования дает существенные преимущества, так как позволяет легко реализовывать сложные команды и исправлять ошибки. Исправления сводятся к замене части микропрограммной памяти и не требуют переделки аппаратуры.

Как правило, одна машинная команда требует для своего выполнения нескольких микрокоманд. Поэтому микропрограммная память должна быть значительно быстрее оперативной, той, в которой хранятся команды и данные. Именно отсутствие достаточно быстрой микропрограммной памяти задержало внедрение микропрограммирования до 1964 г., когда корпорация IBM объявила о создании системы IBM 360, состоящей из нескольких машин. Все они имели одинаковую архитектуру и были микропрограммными. С этого времени началось широкое внедрение микропрограммирования как средства реализации архитектуры. Практически все выпускаемые на продажу машины (за исключением суперкомпьютеров) были микропрограммными, так как микропрограммное управление позволяло экономить дорогое оборудование. Кроме того, оно позволило значительно расширить систему команд, в основном за счет увеличения объема микропрограммной памяти. Внедрение микропрограммирования также стимулировалось необходимостью экономить память, для чего нужны были компактные и мощные команды. В наборе команд процессоров появились такие сложные команды, как “отредактировать”, “транслировать” (IBM 360, 1964 г.), вычисления значения полинома и постановки элемента в двусвязный список (VAX 11/780, 1978 г.). Все это приводило к росту объема микропрограмм. Так, в IBM 360/168 (1973 г.) объем микропрограмм составил 420 Кб при 208 реализованных командах, а в VAX 11/780 фирмы DEC - 480 Кб при 303 командах.

Первыми микропроцессорами, в которых использовались микропрограммы, были i8086 и MC68000.

До 1973 г. операционные системы и системное программное обеспечение писались на ассемблерах соответствующих машин. Только в 1973 г. появилась операционная система Unix, ядро которой почти целиком было написано на разработанном Денисом Ричи и Кеном Томпсоном языке Си. Однако длительное время системное ПО продолжало создаваться на ассемблерах. Например, ОС VMS (1978 г.) была все еще написана на ассемблере. Причиной тому послужила необходимость экономить оперативную память из-за ее высокой стоимости. В последнее десятилетие память настолько подешевела, что отпала необходимость ее экономить. Сейчас трудно представить, что в 1972 г. устройство полупроводниковой оперативной памяти емкостью в 1 Мб стоило 550 тыс. долл. Для сравнения - теперь 5 долл.

В настоящее время большинство программ пишется на языках высокого уровня. Исследования статического и динамического поведения программ, написанных, например, на языках Си и Паскаль, показали, что статически 30 - 40% - это обращения к процедурам, 30 - 40% операторов - присвоения и почти все остальные - условные операторы.

В табл. 1 показаны статические и динамические частоты выполнения различных операторов.

Из табл. 1 следует, что почти в половине случаев обращения к памяти обязаны своим происхождением вызовам процедур и возвратам из них.

Для ускорения выполнения программ желательно минимизировать число обращений к памяти и ускорить вызовы процедур.

Анализ обращений к процедурам показывает, что у 99% всех процедур число параметров не превышает пяти, а у 92% - двух.

При исследовании динамического поведения набора Си программ:

- NROFF - при форматировании руководства по языку Фортран;

- SORT - сортировка массива из 2025 строк;

- Си - компилятор, компилирующий сам себя, оказалось, что при вызове процедур число параметров плюс число локальных переменных не превышает:

- - в 75,4 % случаев;

7 - в 93,8 % случаев;

11 - в 98,6 % случаев;

15 - в 99,2 % случаев;

23 - в 100 % случаев.

Если у каждой процедуры будут свои регистры для передачи параметров и хранения локальных переменных, то при обращении к ним можно сэкономить значительное время.

Практика написания компиляторов и достижения в теории трансляции показали, что для эффективной компиляции лучше иметь небольшой набор простых регистровых команд (и, стало быть, быстрых), чем набор сложных команд, затрудняющих применение методов оптимизации кода транслируемой программы.

Неудивительно, что в реальных программах наиболее часто используются простые команды, такие, как LOAD, STORE, ADD и др., в то время как сложные команды используются весьма редко. Так, в программах для VAX 20% из набора команд занимают при выполнении 0,2% времени, в то же время их объем составляет 60% от общего объема микропрограммной памяти.

Эти соображения послужили основой для создания в начале 80-х годов архитектуры микропроцессоров с сокращенным набором команд (Reduced Instruction Set Computer - RISC-архитектуры).

Введение в архитектуру RISC-процессоров дано в статье Эдуарда Пройдакова на стр. 49.

Исследования в области такой архитектуры были начаты корпорацией IBM в 1975 г. и завершились появлением машины 801; о ней в то время не было публикаций, и поэтому она не оказала влияния на развитие архитектур процессоров.

В университете Беркли были созданы микропроцессоры RISC I и RISC II, первый стал коммерческим микропроцессором MIPS R2000 (1986 г.), а второй превратился в SPARC-1 (1987 г.), в котором имелся набор из 138 регистров, организованных как восемь перекрывающихся окон из 22 регистров; шесть регистров у соседних окон были общими. Через них передавались параметры при вызове процедур.

Впоследствии процессоры RISC-архитектуры были разработаны компаниями Hewlett-Packard - PA RISC (Precision Architecture), DEC - Alpha, IBM, Motorola и Apple - Power PC. Однако процессоры Intel классической CISC-архитектуры - х86 - тоже не стояли на месте. Были выпущены процессоры Pentium, Pentium Pro и Pentium II, не уступающие по производительности процессорам RISC-архитектуры.

От микропроцессоров для высокопроизводительных рабочих станций требуется максимальная производительность, которую можно получить при использовании максимально возможного числа транзисторов, размещаемых на кристалле с приемлемым еще выходом годных микропроцессоров.

Со времен Вавилона и Древнего Египта были известны два способа ускорения выполнения работ:

- увеличение темпа;

- распараллеливание.

В наше время был изобретен конвейер. Работа разбивается на N последовательных этапов, каждый из них поручается отдельному исполнителю. Конвейер позволяет получить N-кратное ускорение, если задание не меняется. В противном случае конвейер перед перезапуском надо очистить, и чем длиннее конвейер, тем больше уходит на это времени.

Увеличение тактовой частоты - основной метод повышения быстродействия микропроцессоров. Например, тактовая частота увеличилась с 5 МГц у процессора i8086 (1978 г.) до 500 МГц у процессора Alpha корпорации DEC (1996 г.) и при этом производительность увеличилась до 500 MIPS. Заметим, что за время такта процессора Alpha свет в вакууме проходит всего 60 см.

Во всех без исключения микропроцессорах для выполнения команд применяется конвейер, число ступеней в котором колеблется от пяти до девяти. Увеличению их числа препятствуют команды передач управления, встречающиеся достаточно часто. Так, в программах для x86 на четыре-пять команд приходится один переход.

Распараллеливание потока команд также используется во всех современных высокопроизводительных процессорах. Число потоков доходит до шести, но в большинстве случаев равно четырем.

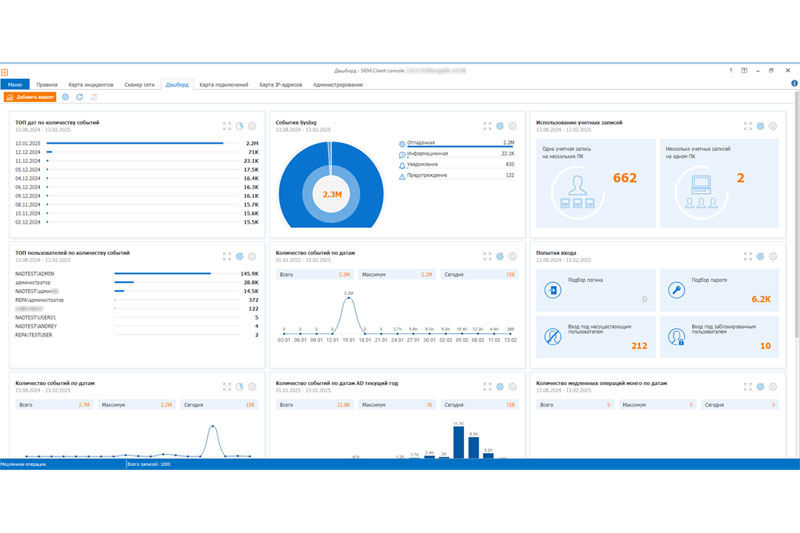

Хорошо известно, что производительность микропроцессора определяется двумя параметрами: логической скоростью, т. е. числом команд, которые микропроцессор выполняет в среднем за такт, и самой тактовой частотой.

Логическая скорость является мерой качества архитектуры и качества ее реализации.

Посмотрим, какова логическая скорость наиболее распространенных в настоящее время микропроцессоров.

Из табл. 2 следует, что максимальная логическая скорость заметно меньше средней.

Чтобы проиллюстрировать трудность ее увеличения, заметим, что в архитектуре х86 ее удвоение достигается лишь при четырехкратном увеличении числа транзисторов.

Перечисленные выше методы повышения быстродействия микропроцессоров ранее применялись в мэйнфреймах. Так, процессор “Эльбрус” (1978 г.):

- декодировал две команды одновременно;

- выполнял команды не в том порядке, в каком они располагались в программе (просматривалось вперед до 30 команд);

- имел спекулятивное выполнение по одному из условных переходов;

- использовал переименование регистров.

Основные производители высокопроизводительных микропроцессоров - это корпорации Intel, Sun Microsystems, DEC, Hewlett-Packard, IBM и MIPS (теперь Silicon Graphics). За исключением корпорации Intel, которая выпускает процессоры архитектуры CISC, все остальные выпускают RISC-процессоры.

Как уже упоминалось, компании MIPS и Sun Microsystems первыми разработали микропроцессоры классической RISC-архитектуры. Само название микропроцессора MIPS расшифровывается как Microprocessor without Interlocked Pipeline Stages, т. е. микропроцессор, у которого нет проверки исполняемых в конвейере команд на зависимость по данным. Это было сделано в соответствии с идеологией максимального упрощения устройства управления.

Часто RISC-процессоры сравнивают с гоночным автомобилем, конструкция которого подчинена цели обеспечения наивысшей скорости при заданном весе. У него нет ничего, без чего можно было бы обойтись.

В первом микропроцессоре MIPS R2000 имелись 32 32-разрядных регистра R0-R31, счетчик команд PC и два дополнительных регистра HI и LO. Регистры с номерами от R1 до R30 - это регистры общего назначения, без специальных функций. Двум регистрам приданы специальные функции:

- При чтении регистра R0 его значение всегда равно нулю. Запись в него любого числа выполняется, а его содержимое не изменяется и остается равным нулю.

- В регистре R31 при выполнении команд “переход” и “переход с возвратом” (JUMP и LINK) запоминается адрес возврата. Тем не менее его можно использовать в любой команде, но с осторожностью.

Так как при выполнении операции целочисленного умножения двух 32-разрядных чисел результат получается 64-разрядным, то для его хранения требуются два регистра. Если результат помещать в регистры общего назначения, то это будет мешать алгоритмам оптимального распределения регистров. Поэтому были введены два специальных регистра HI и LO. При выполнении деления в HI помещается старшая часть делимого, а в LO - младшая. В результате выполнения операции деления частное помещается в LO, а остаток - в HI. В эту же пару записывается результат умножения.

Все команды 32-разрядные. Имеется три формата команд:

- с непосредственным операндом;

- передач управления;

- регистровые.

Наличие команд только трех типов существенно упрощает их декодирование.

Набор команд разделен на пять подгрупп.

- Пересылок данных между памятью и регистрами (Load и Store). Все команды этой подгруппы - с непосредственным операндом. Адрес данного образуется путем сложения содержимого индексного регистра и 16-разрядного смещения со знаком, записанного непосредственно в команде.

- Арифметических команд сложения, вычитания, умножения, деления, сдвигов, а также логических операций, выполняющихся над данными в регистрах.

- Переходов и переходов с возвратом.

- Специальных, среди которых вызов супервизора, контрольные точки и др.

- Обращений к сопроцессору.

Этот первоначальный набор команд (MIPS I) был расширен добавлением команд для вычислений с плавающей запятой. Были добавлены 32 64-разрядных регистра для подобных вычислений двойной точности. Расширенный таким образом набор команд был назван MIPS II. Затем процессор стал 64-разрядным и были добавлены соответствующие команды работы с такими данными, а набор команд стал называться MIPS III. Работа с трехмерными данными потребовала увеличения производительности и набор команд для вычислений с плавающей запятой был соответствующим образом расширен и получил название MIPS VI.

Последнее расширение набора команд для поддержки мультимедиа-данных названо MDMX.

Самый высокопроизводительный микропроцессор компании MIPS Technologies - R10000 - представляет собой суперскалярный процессор, который может выбирать и выполнять до четырех команд за один цикл процессора.

В процессоре имеются два устройства целочисленной арифметики, а также умножитель и сумматор чисел с плавающей запятой. Декодированная команда ставится в одну из трех очередей; две из них - к устройствам целочисленной арифметики и одна - к сумматору и умножителю чисел с плавающей запятой. В каждой очереди производится динамическая диспетчеризация их выполнения. В каждой целочисленной очереди может находиться до 16 команд. За один такт записываются в очередь четыре команды.

Очередь команд вычислений с плавающей запятой имеет емкость в 16 команд. Из очереди команды направляются в сумматор или умножитель. Очередь обладает логикой повторов для выполнения таких команд, как умножение с накоплением. Эти команды вначале направляются в устройство умножения, а затем в сумматор.

Есть отдельная очередь адресов данных, по которым данные выбираются или записываются. Эти адреса направляются в устройство чтения-записи данных (Load-Store). Очередь организована как зацикленный FIFO-буфер. Адреса из него могут браться в произвольном порядке, но должны помещаться и удаляться в исходной последовательности.

Микропроцессор R10000 может работать через кластерную шину в многопроцессорной системе.

64-разрядный процессор PA-8000 компании HP представляет для нас особый интерес, так как имеет наивысшую логическую скорость из всех выпускаемых ныне микропроцессоров, а также потому, что именно в содружестве с HP корпорация Intel разрабатывает процессор Merced.

Каким образом получены такие результаты?

Во-первых, в PA-8000 имеется два устройства целочисленной арифметики, два групповых сдвигателя, два умножителя с накоплением чисел с плавающей запятой, два устройства деления и извлечения квадратного корня и два устройства чтения-записи, которые могут одновременно начать выполнение четырех операций.

Кроме того, существует двухвходовая кэш-память данных и буфер переупорядочивания на 56 команд. Блок выборки команд рассчитан на выборку из внешней кэш-памяти четырех команд за один цикл.

Особые усилия были предприняты для улучшения предсказания адресов передач управления.

В процессоре имеется полностью ассоциативная таблица адресов переходов (BTAC) на 32 адреса, где хранятся адреса совершившихся переходов. При выборке команды ее адрес направляется в кэш-память команд и одновременно в буфер. Если фиксируется совпадение, то адрес, выданный BTAC, используется для выборки следующей команды. Каждый раз, когда адрес перехода предсказан правильно, он помещается в BTAC, если его там не было.

Желательно минимизировать число неудачно предсказанных передач управления. Этой цели служит таблица предсказания адресов переходов (BHT) на 256 входов. Каждый ее элемент содержит 3-разрядный сдвиговый регистр, в котором содержится результат трех предшествующих передач управления, т. е. фиксируется передача. Если две из трех передач совершились, то считается, что и в третий раз она произойдет.

В каждом 64-разрядном устройстве целочисленной арифметики находится и сумматор адресов передач управления.

Устройство для вычислений с плавающей запятой состоит из двух устройств умножения с накоплением (MAC) и двух устройств деления и извлечения квадратного корня.

В процессоре есть аппаратура поддержки отладки и измерений производительности.

Даже краткий обзор архитектурных ухищрений, направленных на увеличение производительности, и скромные результаты этих усилий показывают, что существуют фундаментальные проблемы, препятствующие ее росту. Дело в том, что программист знает, какие части алгоритма могут быть выполнены в программе параллельно и какие операции зависимы друг от друга по данным. Но алгоритм программируется на одном из языков, последовательных по своей природе, вследствие чего зависимости по данным маскируются. Затем программа компилируется и компилятор должен найти части программы, которые можно выполнить параллельно, для чего приходится проводить сложный анализ структуры программы и зависимостей данных друг от друга. В результате компилятор генерирует последовательность команд, максимально использующую возможности параллельного их исполнения на конкретной аппаратуре. А при исполнении этой последовательности суперскалярный процессор должен выполнить почти тот же самый анализ части программы. Это необходимо по нескольким причинам. Во-первых, некоторые команды, например целочисленное деление, в R10000 выполняются за разное время, в зависимости от исходных данных. Во-вторых, в компиляторе могут быть ошибки и он генерирует неоптимальную последовательность команд. И в-третьих, программа может быть просто написана на ассемблере.

Для сложного анализа нужна аппаратура большого объема, что в свою очередь замедляет процессор, а для повышения производительности требуется увеличение числа исполнительных устройств и сложности аппаратуры управления.

Выход из этого положения состоит в разработке архитектуры, в которой на уровне команды явно используется параллелизм. Команда будет состоять из нескольких простых трехадресных регистровых слогов. Все слоги в такой длинной команде, исполняемой за один такт, будут генерироваться компилятором.

Есть основания полагать, что таким путем можно довести среднюю логическую скорость до четырех.

Главная проблема новой архитектуры - совместимость с ранее написанными программами.

Существует и другой подход, когда в микропроцессор помещаются несколько процессоров и аппаратура координации их совместной работы.

Проект создания такого процессора - М-машины - близится к завершению, он разрабатывается в Массачусетском технологическом институте.

М-машина Массачусетского технологического института

В рамках программы Mechanisms for Teraflops, финансируемой DARPA, в Массачусетском технологическом институте разрабатывается компьютер новой архитектуры, или М-машина, состоящая из нескольких обрабатывающих узлов, соединенных в сеть. Цель разработки - создание компьютеров с терафлопной производительностью.

Каждый узел состоит из микропроцессора с несколькими арифметическими устройствами (MAP) и пятью устройствами динамической памяти. Микропроцессор MAP содержит семь обрабатывающих устройств, разделенных на три кластера. В кластере помещено целочисленное арифметическое устройство, память и группа регистров. Кроме того, в микропроцессоре имеются устройство управления сетью, организующее двухмерную сеть, общая кэш-память, интерфейс с оперативной памятью и два набора шин, через которые можно осуществлять запись данных из кластера в кластер и передачу данных между кластерами и памятью.

М-машина позволяет одновременно на трех кластерах выполнять последовательности команд (треды).

Схема защиты памяти базируется на защищенных указателях, используемых для предотвращения неавторизованного доступа к памяти из нескольких тредов, которые могут одновременно выполняться на М-машине. Указатели реализованы в виде 64-разрядных тегированных слов. В них закодированы права доступа, адреса и информация о сегментах. Размещение прав доступа вместе с адресом позволяет разделить функции защиты и трансляции адреса. Такая схема дает возможность процессору MAP одновременно в одном цикле обращаться к памяти из различных доменов.

Микропроцессор, содержащий 5 млн. транзисторов, будет изготовлен по 0,5 нм КМОП-технологии на кристалле размером 18,25х18,30 мм.

Первые микропроцессоры будут готовы в первом квартале 1998 г., а М-машина, изготовленная на их основе, - во втором.

для мобильных устройств

Существует рынок микропроцессоров для мобильных устройств, таких, как карманные и блокнотные компьютеры, персональные коммуникаторы, “умные” мобильные и Интернет-телефоны и т. п. Микропроцессоры для этих устройств должны иметь малое энергопотребление и высокую производительность. Здесь главный критерий - производительность в расчете на ватт потребляемой мощности (табл. 3).

Из процессоров такого класса заслуживает внимания микропроцессор ARM, разработанный в 1988 г. английской компанией ACORN. Его архитектура - классический RISC. Аппаратура процессора состоит из 32-разрядного арифметически-логического устройства, группового сдвигателя, умножителя Бута, сумматора адресов и регистрового файла из 25 регистров, позволяющего за один такт прочитать два и записать один регистр. Для ускорения выполнения команд в процессоре реализован трехступенчатый конвейер. В каждом такте одновременно одна команда выбирается, одна декодируется и одна выполняется. Все команды имеют одинаковую длину в 32 разряда. Арифметические команды - трехадресные регистровые и выполняются за один такт.

Рис.3 Микрофотография процессора SA-1100

Как и должно быть в RISC-процессоре, команды обращения к памяти - только загрузка в регистр и выгрузка из него.

Старшие четыре разряда команды представляют код условия, при котором данная команда выполняется. Такая схема позволяет во многих случаях обойтись без использования команд условного перехода, тормозящих конвейер.

Процессор был выполнен по 3-микронной КМОП-технологии и содержал 27 тыс. транзисторов, причем управление занимало 4 % площади кристалла.

Однако на реальных задачах при тактовой частоте в 8 МГц этот процессор не уступал по скорости 16 МГц 386-му процессору. При напряжении питания 5 В он потреблял 10 мА.

Кроме процессора были разработаны диспетчер памяти, контроллеры ввода-вывода и дисплея. Этот набор микросхем применялся в ПК “Архимед”.

В ноябре 1990 г. компании ACORN, VLSI Technology и Apple образовали фирму ARM. Первоначально предполагалось разрабатывать дешевые, но производительные процессоры для образовательной сферы.

Архитектура оказалась настолько удачной, что легла в основу целого семейства микропроцессоров и микроконтроллеров, в том числе микропроцессоров ARM7, ARM6 и ARM60. Они идеальны для применения в условиях ограниченных возможностей источников питания.

В таблице 4 представлены их параметры.

Многие компании купили лицензии на архитектуру ARM. В том числе: Digital Semiconductor, Cirrus Logic, Samsung, NEC, Hyundai, LG Semicon, Lucent Microelectronics, OKI, Philips, Texas Instruments и др.

Корпорация Digital Semiconductor в 1996 г. выпустила микропроцессор StrongARM (SA-110), представляющий собой расширенную реализацию архитектуры ARM версии 4. В нем, в частности, имеется: пятиступенчатый конвейер; диспетчер памяти; кэш-память команд и данных по 16 Кб.

Процессор работает с тактовой частотой 100, 160 и 200 МГц, его производительность - 115, 185 и 230 MIPS. Потребляемая мощность на частоте 160 МГц - 450 мВт.

2 сентября 1997 г. компания выпустила SA-1100 - 32-разрядный микропроцессор с кэш-памятью команд объемом 16 Кб, кэш-памятью данных объемом 8 Кб, диспетчером памяти, контроллерами жидкокристаллического дисплея, динамической памяти, прямого доступа и пятью портами последовательных каналов (рис. 3). Число транзисторов в нем - 2,5 млн.

Процессор работает на тактовой частоте 133 и 200 МГц со скоростью 150 и 230 MIPS, потребляя при этом соответственно 200 и 250 мВт.

В третье тысячелетие мы войдем с процессором Intel с большим числом исполнительных устройств (целочисленной и плавающей арифметики и вычислений с плавающей запятой, а также устройств обработки мультимедиа-данных), с длинной командой, в которой на уровне входного языка явным образом будет учитываться параллелизм. 4