Леонид Черняк

Почему процессор Merced, выпуск которого ожидается в 1999 г., назван именно так, неизвестно, но на ум приходит аналогия с близким по звучанию названием престижных автомобилей “Мерседес”. И кто знает, может быть, этот процессор окажет на компьютерный рынок влияние не меньшее, чем в свое время “Мерседес” на автомобильный.

Фрэнк Бэтке

И хотя до появления нового процессора еще около года, уже сегодня с достаточной достоверностью можно предсказать последствия этого события. Merced, безусловно, нарушит нынешнее относительно уравновешенное состояние на рынке RISC-процессоров. Совершенно очевидно, что из существующих пяти - шести продуктов этого класса останется не более двух - трех. Учитывая грядущие перемены, большинство производителей заблаговременно готовятся к ним, каждый в меру своих возможностей.

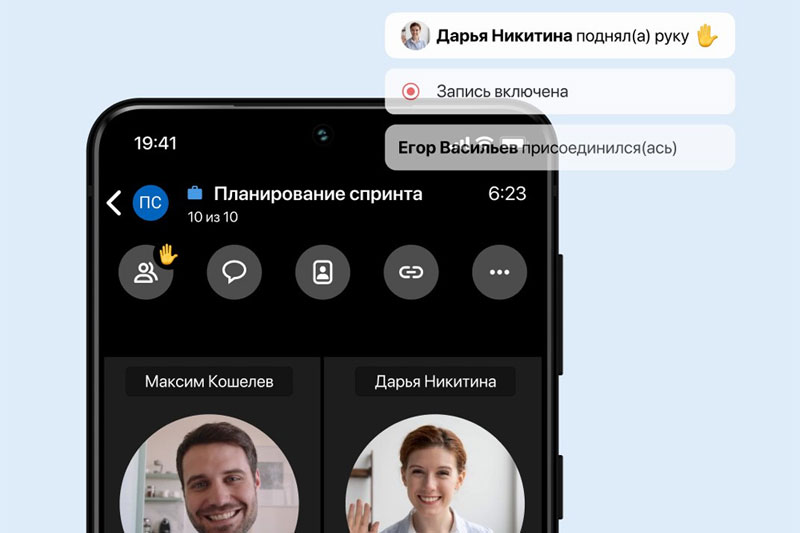

Позиция Hewlett-Packard в свете грядущих изменений отличается от позиции большинства других компаний в силу того, что HP кооперируется с Intel в разработке нового микропроцессора. 16 апреля в Москве состоялась пресс-конференция, тема которой была обозначена, как “Развитие микропроцессорной базы Hewlett-Packard”.

Фрэнк Бэтке, директор HP по маркетингу высокопроизводительных вычислительных систем раскрыл некоторые особенности архитектуры будущих процессоров Merced.

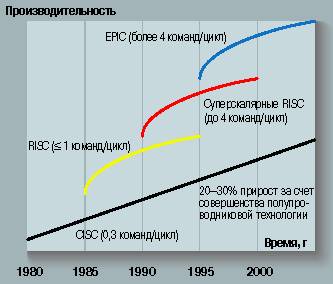

Приступая к созданию нового продукта, разработчики ставили перед собой цель повысить производительность процессоров. Упрощенно - производительность процессора есть произведение тактовой частоты на количество действий, выполняемых за один такт. Из графика на рисунке видно, что рост производительности этих устройств определяется двумя факторами: первый - повышение тактовой частоты (оно основано на прогрессе полупроводниковой технологии и имеет линейный характер) и второй - рост количества действий за один такт (он является производным от совершенствования архитектуры).

Процессоры PA8x00 производства HP имеют наибольшее число арифметических устройств для выполнения операций с плавающей и фиксированной точкой; они в большей степени, чем другие RISC-процессоры, адаптированы к нарушению линейной последовательности при выполнении инструкций (out-of-order). За несколько лет, в течение которых выпускаются PA8x00, компанией накоплен опыт достижения высокой производительности не только путем наращивания тактовой частоты, но и за счет совершенства логических и арифметических характеристик процессора. Именно этот архитектурный опыт и оказался востребованным в совместной разработке с Intel, где сошлись две школы разработки процессоров.

Технология EPIC

Сегодня суперскалярные процессоры могут выполнять до четырех команд в одном цикле. Однако, по мнению специалистов Hewlett-Packard, в начале следующего века возможности архитектуры RISC-процессоров будут исчерпаны. На смену ей придет технология следующего поколения, получившая название “вычисления с явным параллелизмом команд” (Explicitly Parallel Instruction Computing, EPIC).

Уточним значение некоторых терминов, связанных с будущими процессорами. EPIC - это название технологии (подобно RISC или CISC), IA-64 - наименование одной из архитектур (как IA-32 или PA-RISC), наконец, Merced - это всего лишь название одного из процессоров (подобно Pentium или PA-8500).

Очень часто под словом “Merced” подразумевается архитектура IA-64, которая создана совместно Hewlett-Packard и Intel. Использование в ее названии числа 64 не связано с форматом команд, оно указывает только размер адресного регистра и соответственно пространство прямо адресуемой памяти.

Г-н Бэтке рассказал о некоторых основных характеристиках IA-64. В ней, в частности, используется 128 регистров общего назначения и столько же регистров для выполнения операций с плавающей точкой. Количество и тех и других является фиксированной величиной. В то же время число арифметических и логических устройств, которые могут быть к ним подключены, зависит от конкретного типа процессора. IA-64 позволяет создавать процессоры с различной вычислительной мощностью, и теперь появляется возможность говорить о масштабировании процессоров. До сих пор под термином масштабирование подразумевалась возможность увеличения числа процессоров. В рамках одной архитектуры IA-64 может выпускаться несколько типов процессоров разной производительности и соответственно стоимости, ориентированных на разные приложения.

Появление процессоров, различающихся по производительности, нарушает привычную схему. Сильная сторона предыдущих поколений процессоров Intel состояла в том, что большой системный “дом”, как бы велик он ни был, строился из унифицированных “кирпичей”. Одни и те же процессоры использовались и в персональных компьютерах, и в мультипроцессорных серверах. IA-64 позволяет создавать строительные блоки, размер которых можно изменять и выбирать те, что соответствуют определенному классу системы. Естественно, что процессоры при этом сохраняют бинарную совместимость.

Еще одна принципиальная новая составляющая архитектуры IA-64 - понятие bundle (связка). Каноническая схема работы процессора предполагает выполнение команд в определенной последовательности. Суперскалярные процессоры отличаются тем, что несколько команд выполняется одновременно. IA-64 делает следующий шаг в этом направлении. Связка дает возможность выполнить за один такт еще большее число команд.

В IA-64 связка становится основной исполняемой единицей, в нее “упакованы” отдельные команды. Длина связки составляет 128 бит, она состоит из четырех полей: трех команд и специального служебного поля - шаблона (template). Сведения о формате и системе команд пока не разглашаются. Но о функции шаблонов известно, что она заключается в управлении исполнением команд, входящих в связки, и в объединении нескольких связок в одну суперсвязку. Принципиально важно то, что команды, входящие в связку, могут быть распараллелены между множеством арифметических и логических устройств, включенных в состав процессора, и выполнены за один такт.

Шаблон играет роль своего рода посредника между этапами компиляции и выполнения. Благодаря содержимому шаблонов скомпилированная программа несет в себе информацию о том, как она должна выполняться. Значения шаблонов устанавливаются компилятором, он определяет последовательность выполнения команд в данной связке и (обеспечивает их взаимодействие с другими связками).

Возможность включения в состав скомпилированной программы управляющей информации видоизменяет процесс компиляции. Помимо обычной задачи перевода текста программы в машинный код появляется необходимость выполнить еще один этап, а именно: оптимизировать выполнение с максимальным параллелизмом. На этом этапе компилятор формирует содержание шаблонов.

Эволюция процессорных технологий

До определенного времени Merced, так же как его автомобильный собрат, будет рассчитан на “средний и высший класс” потребителей. Пользователи персональных компьютеров несколько лет могут жить вполне спокойно: привычной архитектуре IA-32 обеспечено еще много лет жизни, а Merced до поры, до времени - не для них.